在當今數(shù)字化與智能化浪潮席卷全球的時代,集成電路(IC)作為信息技術(shù)的基石,其設計與制造水平直接決定了電子系統(tǒng)的性能與創(chuàng)新高度。其中,模擬集成電路因其處理連續(xù)信號的關(guān)鍵作用,在通信、傳感、電源管理等領(lǐng)域不可或缺。而版圖設計作為連接電路設計與芯片制造的橋梁,是決定芯片性能、可靠性及成本的核心環(huán)節(jié)。《芯片設計——CMOS模擬集成電路版圖設計與驗證:基于Cadence IC 6》這套正版兩冊著作,正是聚焦于這一關(guān)鍵技術(shù)領(lǐng)域,為工程師、研究人員及高校學子提供了系統(tǒng)、深入且實用的指導。

本書以主流的CMOS工藝為背景,全面闡述了模擬集成電路版圖設計的基本原理、設計方法與工程實踐。內(nèi)容從半導體物理與工藝基礎入手,清晰解釋了MOS器件特性、寄生效應、工藝偏差等對版圖設計的影響,為后續(xù)的實踐操作奠定了堅實的理論基礎。重點講解了各種模擬電路模塊(如運算放大器、基準電壓源、比較器、數(shù)據(jù)轉(zhuǎn)換器等)的版圖設計技巧,涵蓋了匹配性設計、噪聲抑制、抗干擾布局、電源與地線規(guī)劃、ESD保護等關(guān)鍵議題。作者不僅闡述了“如何做”,更深入分析了“為何如此做”,幫助讀者建立起面向性能優(yōu)化的設計思維。

本書最大的特色在于其極強的實踐性與工具導向性。它深度整合了全球EDA(電子設計自動化)領(lǐng)導者Cadence公司的IC 6系列設計工具。通過循序漸進的教學案例,詳細展示了使用Virtuoso平臺進行原理圖輸入、版圖編輯、物理驗證(DRC、LVS)、寄生參數(shù)提取(PEX)以及后仿真的完整流程。讀者可以跟隨步驟,親手實踐從電路圖到最終可交付制造(GDSII)數(shù)據(jù)文件的整個設計周期,深刻理解工具命令、設計規(guī)則文件(DRC/LVS Deck)的編寫與解讀,以及如何利用工具發(fā)現(xiàn)并解決設計中的實際問題。這種基于業(yè)界標準工具鏈的實戰(zhàn)訓練,極大縮短了理論學習與工程應用之間的距離。

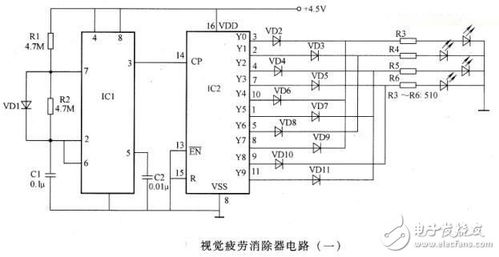

本書還對版圖驗證環(huán)節(jié)給予了高度重視。除了基礎的DRC(設計規(guī)則檢查)和LVS(版圖與原理圖一致性檢查)外,還探討了針對模擬電路特性的專項驗證,如天線效應檢查、電遷移分析、襯底噪聲耦合評估等。這些內(nèi)容確保了設計不僅在物理上可制造,更能在電學性能上滿足苛刻的指標要求。

總而言之,這套《芯片設計——CMOS模擬集成電路版圖設計與驗證:基于Cadence IC 6》雙冊教材,結(jié)構(gòu)嚴謹,內(nèi)容翔實,理論與實踐并重。它不僅是初學者步入模擬版圖設計殿堂的優(yōu)質(zhì)指南,也是資深工程師深化理解、解決復雜設計難題的寶貴參考書。在芯片國產(chǎn)化與自主創(chuàng)新需求日益迫切的大背景下,掌握本書所傳授的知識與技能,對于培養(yǎng)高端集成電路設計人才、提升我國芯片產(chǎn)業(yè)的核心競爭力具有重要的現(xiàn)實意義。