集成電路設(shè)計(jì)是現(xiàn)代電子技術(shù)的核心,而CMOS技術(shù)作為其中的主流,廣泛應(yīng)用于各類電子設(shè)備中。本文將介紹CMOS集成電路設(shè)計(jì)的基本概念、設(shè)計(jì)流程、關(guān)鍵技術(shù)及其未來發(fā)展方向。

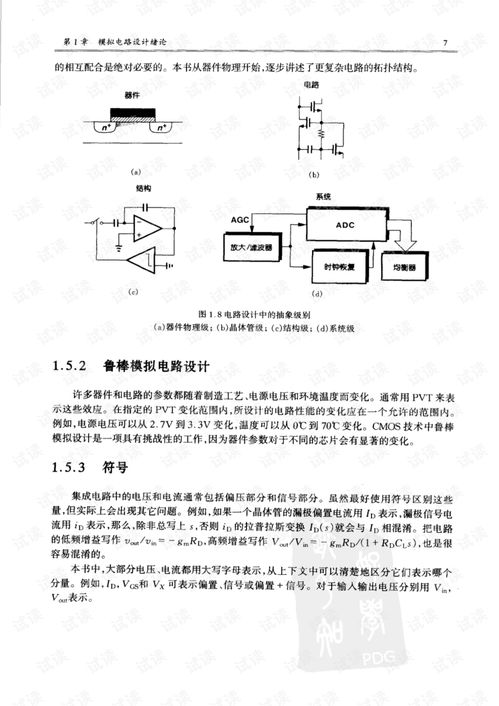

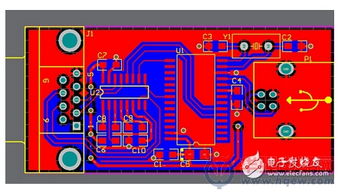

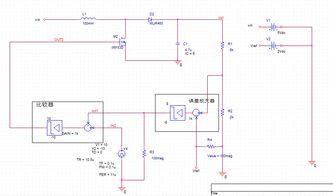

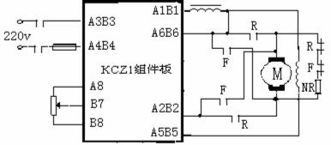

CMOS集成電路設(shè)計(jì)基于互補(bǔ)金屬氧化物半導(dǎo)體技術(shù),其低功耗、高集成度和良好的抗干擾能力使其成為數(shù)字和模擬電路設(shè)計(jì)的首選。設(shè)計(jì)過程通常包括需求分析、架構(gòu)設(shè)計(jì)、邏輯設(shè)計(jì)、物理實(shí)現(xiàn)和驗(yàn)證等階段。在需求分析階段,設(shè)計(jì)師需明確電路的功能、性能和功耗指標(biāo);架構(gòu)設(shè)計(jì)則涉及整體模塊劃分和接口定義;邏輯設(shè)計(jì)使用硬件描述語言實(shí)現(xiàn)電路功能;物理實(shí)現(xiàn)包括布局布線,確保電路在芯片上的正確實(shí)現(xiàn);驗(yàn)證階段通過仿真和測(cè)試確保設(shè)計(jì)符合要求。

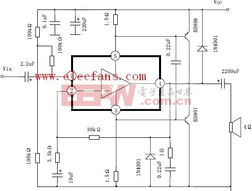

關(guān)鍵技術(shù)在CMOS集成電路設(shè)計(jì)中至關(guān)重要。例如,低功耗設(shè)計(jì)技術(shù)如電源門控和動(dòng)態(tài)電壓頻率調(diào)節(jié),可顯著降低能耗;時(shí)序分析和時(shí)鐘樹綜合確保信號(hào)同步;設(shè)計(jì)自動(dòng)化工具如EDA軟件提升了設(shè)計(jì)效率。隨著工藝節(jié)點(diǎn)不斷縮小至納米級(jí)別,設(shè)計(jì)師需應(yīng)對(duì)短溝道效應(yīng)和互連延遲等挑戰(zhàn)。

CMOS集成電路設(shè)計(jì)正朝著更高集成度、更低功耗和異構(gòu)集成方向發(fā)展。新興技術(shù)如3D集成電路和AI輔助設(shè)計(jì)將推動(dòng)行業(yè)創(chuàng)新。CMOS集成電路設(shè)計(jì)不僅是技術(shù)進(jìn)步的引擎,也是推動(dòng)智能社會(huì)發(fā)展的關(guān)鍵力量。