射頻電路設計實訓和集成電路設計是電子工程領域的關鍵環節,涉及高頻信號處理、芯片布局及系統集成。無論是在實訓中還是在專業設計中,都需要遵循一定的原則和注意事項,以確保電路的性能、可靠性和效率。以下將分射頻電路設計實訓和集成電路設計兩部分,詳細闡述需要注意的關鍵點。

一、射頻電路設計實訓的注意事項

射頻電路設計實訓通常在實驗室環境中進行,旨在讓學生或工程師掌握高頻電路的設計、仿真和測試技能。注意以下幾個方面:

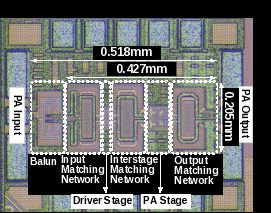

- 理論基礎扎實性:射頻電路工作在高頻范圍(如幾百MHz到幾十GHz),需要深入理解傳輸線理論、史密斯圓圖、阻抗匹配等概念。實訓前應復習相關理論,如S參數、噪聲系數、穩定性分析,避免因理論薄弱導致設計錯誤。

- 仿真工具的正確使用:常用仿真軟件如ADS、HFSS或CST。實訓中需注意:

- 準確設置頻率范圍和邊界條件。

- 進行參數掃描和優化,確保電路性能(如增益、帶寬)符合要求。

- 驗證仿真結果與實際測試的一致性,避免過度依賴仿真而忽略實際效應。

- PCB布局與接地設計:射頻電路對布局敏感,實訓時需注意:

- 使用高頻板材(如ROGERS),減少介電損耗。

- 保持信號路徑短而直,避免交叉和環路,以減少串擾和輻射。

- 采用多點接地或接地平面,確保低阻抗返回路徑,防止地彈和噪聲。

- 測試與測量技巧:實訓中常涉及網絡分析儀、頻譜分析儀等設備。注意事項包括:

- 校準儀器,消除系統誤差。

- 使用合適的探頭和電纜,避免引入額外損耗或反射。

- 注意環境干擾,如電磁干擾(EMI),必要時使用屏蔽箱。

- 安全與文檔記錄:高頻設備可能產生輻射,實訓中需遵守安全規范。詳細記錄設計過程、仿真數據和測試結果,便于問題分析和改進。

二、集成電路設計的注意事項

集成電路設計涉及將多個電路元件集成到單一芯片上,需要綜合考慮性能、功耗、面積和成本。以下是一些關鍵注意事項:

- 設計規范與流程:遵循標準設計流程,如從規格定義、架構設計、RTL編碼到物理實現。注意:

- 明確設計目標,如速度、功耗或面積優先。

- 使用EDA工具(如Cadence、Synopsys)進行仿真和驗證,確保功能正確。

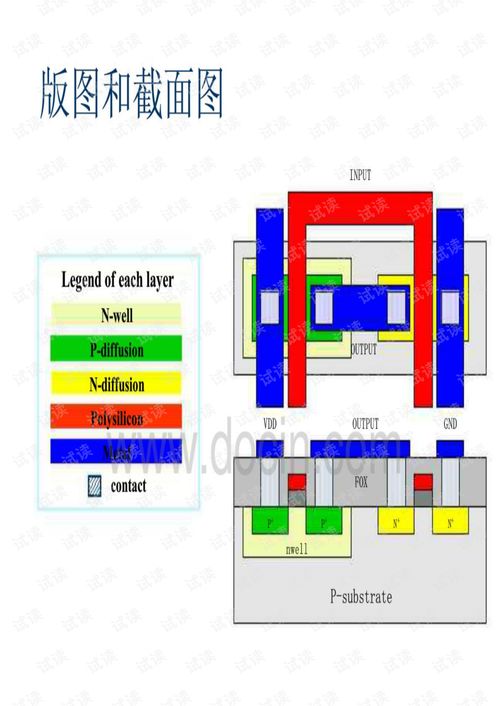

- 工藝選擇與約束:根據應用選擇合適工藝節點(如CMOS、BiCMOS)。注意事項:

- 考慮工藝變異和溫度影響,進行角落仿真(corner analysis)。

- 優化晶體管尺寸和布局,減少寄生效應。

- 電源與噪聲管理:集成電路中電源完整性和信號完整性至關重要:

- 使用去耦電容和電源網格,減少電壓降和噪聲。

- 隔離模擬和數字電路,防止 substrate 噪聲耦合。

- 測試與可測性設計:在設計階段集成測試結構,如掃描鏈或BIST(內置自測試),以方便量產測試和故障診斷。

- 團隊協作與文檔化:集成電路設計常涉及多團隊合作,需保持清晰溝通和文檔記錄,避免設計沖突或誤解。

總結

射頻電路設計實訓和集成電路設計都需要理論與實踐結合。實訓中注重動手能力和問題解決,而專業設計則強調系統優化和可制造性。通過注意上述要點,可以提升設計成功率,減少返工風險。無論是學生還是工程師,持續學習和實踐都是關鍵。